As the number of available qubits in a quantum computer increases, the power of the quantum computer increases exponentially thanks to the rapidly increasing size of the computational space: adding one additional qubit doubles the size of the computational space the quantum computer can access.

IonQ’s quantum computers use trapped atomic ions as qubits: these qubits are perfectly identical with no “manufacturing variations.” They are in fact atomic clocks, so stable and replicable that such systems form the basis for time standards throughout the world. These ideal qubits are assembled into a linear chain using an ion trap chip, and single qubit gates on any qubit as well as two-qubit gates between an arbitrary pair of ions are implemented by tailoring the laser beams that drive the gates. The beauty of this approach is that we can achieve all-to-all connectivity among the qubits in an ion chain, allowing us to efficiently run quantum algorithms with arbitrary structures. Examples of research papers that demonstrate this advantage are found here: Experimental comparison of two quantum computing architectures (Linke et al.,2017), Architecting Noisy Intermediate-Scale Quantum Computers: A Real-System Study (Murali et al., 2020).

Such a chain can be considered a (single-core) quantum processing unit (QPU), akin to the classical central processing units (CPUs). The size of an individual QPU in current IonQ systems is determined by the number of qubits in the chain. In classical CPUs, we understand the benefits of going to a larger-scale processor: while a 64-bit processor can be constructed from several 8-bit processors (even from individual logic gates), the computational efficiency is much higher with a single 64-bit processor. Increasing the bit size of a single core CPU has stalled over the past decade as the cost-to-benefit ratio of building and deploying a 128-bit processor is not clear: the complexity of the connections within the processor increases dramatically as it scales, but the benefits increase, at best, linearly in a classical CPU. Instead, today we get dual-core, quad-core, six-core and eight-core processors, where multiple 64-bit processor cores are integrated into a single chip with communication provided among the cores.

Similar to classical CPUs, the size of IonQ’s individual QPU is limited by the high-fidelity entangling gates that can be deployed over the length of the chain. While advances in technology can continue to improve the size of each QPU, we do anticipate a practical size limit in our QPUs due to the growing complexity in connectivity. (Such a limitation is likely to hold in any quantum computer technology.) IonQ’s next step in scaling strategy is to build multicore QPUs, placing multiple processing cores in one chip just like the multicore CPUs. Similar to the multicore CPUs, we need to ensure (quantum) information is shared among the cores. However, unlike the multicore CPUs where dual- and quad-cores correspond to about twice and four times the computational power, respectively, multicore QPUs can increase the computational power exponentially if properly architected.

IonQ’s approach to multicore QPUs is based on the notion of the Reconfigurable Multicore Quantum Architecture (RMQA). The technical foundation of manipulating multiple ion chains is based on the pioneering work in 2002 by IonQ co-founder and Chief Scientist Chris Monroe, and his colleagues at the National Institute of Standards and Technology including Nobel Laureate and IonQ technical advisor Dr. David Wineland. They first proposed the quantum charge-coupled device (QCCD) architecture, where the technology for shuttling ions and ion chains in a complex trap chip was outlined.

.jpeg)

In RMQA, multiple ion chains are manipulated to dynamically form quantum computing cores. The figure above shows an example of four ion chains of 16 ions each, comprised of 12 qubit ions and 4 refrigerant ions (schematically shown in blue and red in the top figure). We start with trapping four such chains, as shown in Configuration (1). To form the first quantum computing core, the two right-most chains are combined into a 32-ion chain, on which arbitrary quantum computations can be performed, as in Configuration (2). Once part of the computation is complete, the trap chip reconfigures the ion chains into Configuration (3), where the middle two chains are now combined into a single quantum computing core. Further quantum processing can be performed on this core. Similarly, the trap chip can reconfigure the chains yet again, as shown in Configuration (4), where the two left-most chains form the quantum processing core. Using this approach of reconfigurable cores, one can utilize the full computational space spanned by all qubit ions in the system, increasing the computational power exponentially. The addition of each chain increases the computational space by a factor of 2^12 = 4,096. The reconfigurable multicore QPU discussed in this example will support 48 highly connected qubits in a single processor.

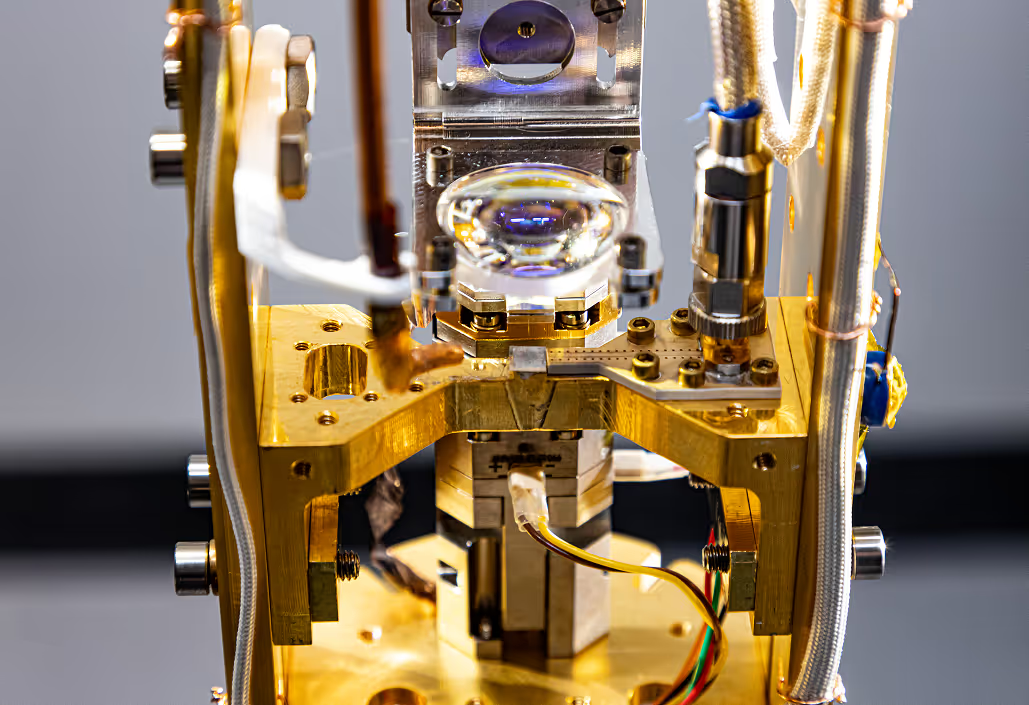

In addition to reconfiguring the ion chains into a single quantum computing core at a time, the trap chips can configure the ion chains into multiple simultaneous quantum computing cores, allowing for parallel quantum operations among each of these cores, as shown in Configuration (5). The total number of qubits in the RMQA can be increased by either increasing the number in each chain of ions or by increasing the number of chains. IonQ has established the trap chip technology to realize such RMQA with the utmost precision and stability, as was released in a technology demonstrator today.

Expect to see RMQA integrated into IonQ systems in the near future, building on IonQ's current leadership in single core QPUs. Starting with this demonstration, IonQ has laid the foundation for increased qubit counts into the triple digits on a single chip, as well as future Parallel Multicore Quantum Processing Units.